网络上一般针对于WiFi/BT模组布局布线要求如下:

(1)WiFi/BT模块属于易受干扰的模块,PCB Layout时,注意远离电源、DDR等模块,空间充足的情况下建议添加屏蔽罩。

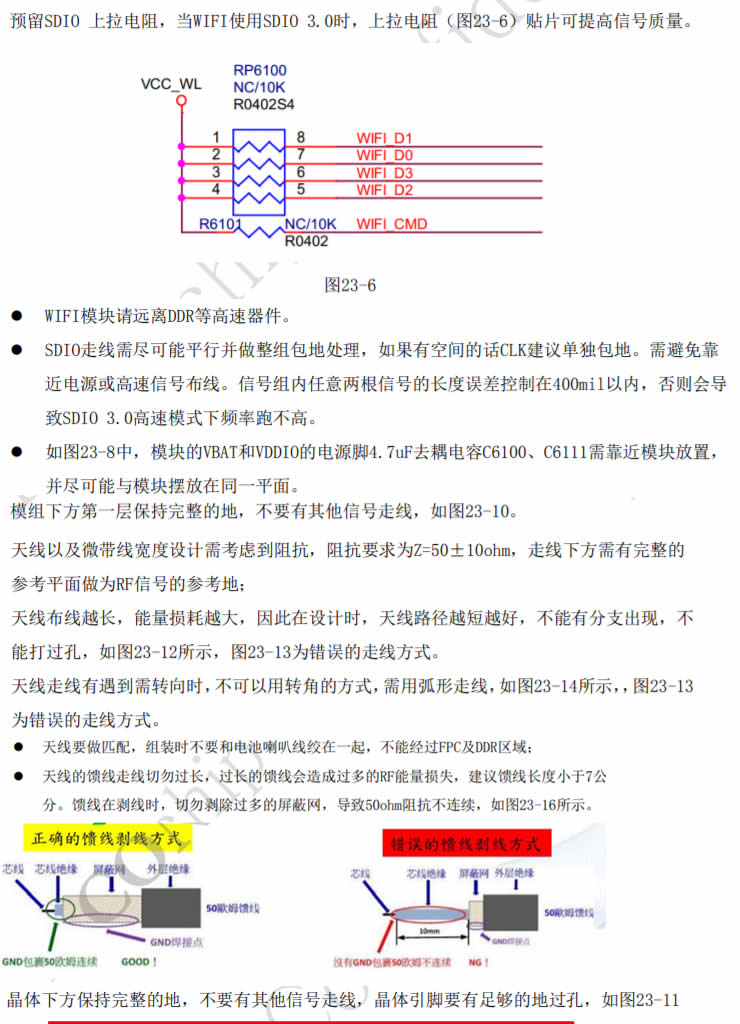

(2)SDIO一组的信号线保证走在完整地参考的信号层,不跨分割,同组同层,然后整组进行包地处理,有空间的情况,CLK信号进行单独包地处理,尽量避开高速信号线和电源区域,拉大与其他信号线间的间距。

(3)整组的SDIO信号线进行等长处理,以CLK信号作为参考目标线,误差控制在300mil以内,总的长度控制在12inch以内,尽量缩短走线的长度,以提高SDIO接口的兼容性和稳定性。

(4)同样是为了避免干扰,模组下方第一层保持完整的地,不要有其他信号走线,其他走线尽量走在内层。

(5)晶体下方保持完整的地,不要有其他信号走线,晶体引脚要有足够的地过孔进行回流。

(6)天线及微带线宽度设计需考虑到阻抗,阻抗严格为Z = 50 ±10 Ω,第一种采取共面阻抗设计,参考相邻的层,走线下方有完整的地作为RF信号的参考地;第二种采取隔层参考,参考相邻的第二层,相邻层天线走线部分挖空,相邻的第二层有完整的地作为参考地即可。走线下方需有完整的参考平面作为RF信号的参考地,天线布线越长,能量损耗越大,因此在设计时,天线路径越短越好,不能有分支出现,不能打过孔。天线走线需要转向时,不可以用转角的方式,应弧形走线。

(7)天线部分走线周围有尽量多的大地过孔,远离其他信号线,天线区域越干净越好。

瑞芯微给的参考设计指导: RK3288+Hardware+Design+Guide+V10-20140625

RK3288+Hardware+Design+Guide+V10-20140625

瑞昱给的参考设计建议:

- 模组GND pin与main board连线加粗

- 模组是几层版?2L模组,main board模组下放表层最好不要走线,最好是模组旋转180度,天线改到下面,SDIO走在模组下面会有影响

- SD_CLK单独包地,SDIO整组包地,至少SD_CLK在靠近wifi这边预留RC

- 尽量避免这种破碎的小块铜皮,会有天线效应